以AI為核心的異質整合技術革命:AI時代的硬體焦慮

在人工智慧應用以迅雷不及掩耳的速度席捲全球之際,其帶來的挑戰也不容小覷。在眾人都關注AI軟體發展 (像機器學習ML技術) 的時候,硬體的難處也不容忽視。AI時代的硬體焦慮是:軟體一直在進步,硬體能跟上嗎?

傳統的摩爾定律(每兩年晶體管數量倍增)已逐漸放緩,單晶片的製程極限與成本已近天花板。因此,下一代AI硬體的發展,必須另闢蹊徑。AI的創新,不能只靠演算法與模型,硬體創新必須跟上,甚至領先。Swaminathan教授表示,當摩爾定律已不再是黃金定律時,異質整合正帶領我們走向摩爾的下一站。

扇出型封裝正變得無處不在

集微諮詢(JW insights)認為:

▲ 扇出型封裝 (Fan-out Panel Level Packaging, FOPLP) 因為能夠提供具有更高I/O密度的更大晶片,大幅減少系統的尺寸,正成為應對異構整合挑戰的不二之選;

▲ 當FOPLP技術進一步成熟,有越來越多類型的廠商參與進來的時候,扇出型封裝可能會迎來全面的爆發。

由於摩爾定律在7nm以下已經難以維持以前的速度,後端封裝技術對於滿足對低延遲、更高頻寬和具有成本效益的半導體晶片的需求變得越來越重要。而扇出型封裝因為能夠提供具有更高I/O密度的更大晶片,大幅減少系統的尺寸,正成為應對異構整合挑戰的不二之選。

...

新加坡IME:以異質整合先進封裝技術推動AI及HPC的運算大未來

新加坡微電子研究院(IME)異質整合部門主管Vempati Srinivasa Rao 於「2025異質整合藍圖第8屆年會」壓軸演出,發表了 "Bridging Technologies in AI: From Chip Design to Advanced Packaging and System Integration" 報告 。《報告 》 指出,未來要實現Zettascale等級的AI與HPC處理效能,一個封裝構件中可能需要容納超過一兆個晶體管。這意味著傳統單晶片設計必須讓位給由多顆小晶粒(chiplets)所組成的大規模系統級封裝,而晶粒之間的互連方式,將直接影響系統的頻寬、延遲、功耗與可靠性。

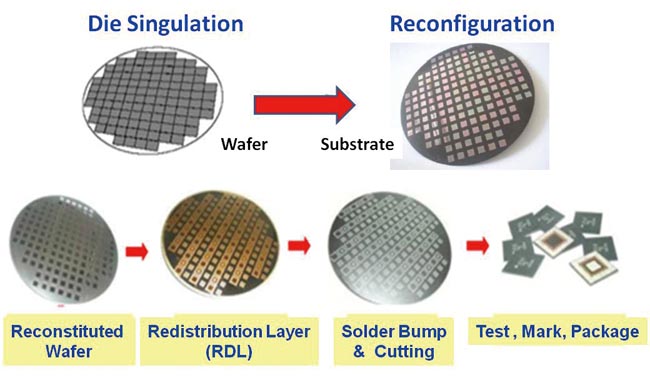

散出型晶圓級構裝 (Fan-Out WLP)之技術與挑戰

由於消費性電子產品對於可攜式(Portability)及多功能(Multi-function)之需求,迫使微電子構裝發展朝小尺寸、高性能、及降低成本前進。晶圓級構裝(Wafer Level Package; 簡稱WLP)具備縮小構裝尺寸之優勢,剛好迎合行動電子產品之市場趨勢。

然而,傳統WLP構裝是將晶片的I/O點,經由散入(Fan-In)技術將凸塊以矩陣式( Area Array)排列於晶片面積內,簡稱為Fan-In WLP。然而,決定晶片是否可採用散入(Fan-In)技術構裝之前,必須同時評估元件尺寸、I/O接點數及間距等因素,進而確認晶片是否有足夠的空間容納所有的連接點。

前段I...

大陸先進封裝「風雲再起」

儘管封裝業算是大陸半導體業的「最強項」,但伴隨著先進封裝的演進,以及各方勢力紛紛拍馬趕到,先進封裝江湖「風雲再起」。

據Yole Developpement的數據顯示,2018年到2024年,先進封裝市場的複合年成長率為8.2%,預估在2025年先進封裝將佔據整個市場的半壁江山。細究其驅動力,正是由於先進封裝可提高封裝效率,降低封裝成本,提供更好的封裝性價比,正以不可阻擋之勢成未來封測行業的主流。相應地,圍繞先進封裝的「搶位賽」亦愈演愈烈。

進階

追溯起來,半導體封裝技術的發展可分為四個階段,從最初的DIP到PGA,再到BGA、CSP,再進階到如今先進封裝風行,包括倒裝晶片(FC...

【為台灣加油打氣專欄】利用非線性光學的SiC基板檢測技術

在過去,半導體基板都是用矽半導體,但是如果要製造應付高頻及高功率的晶片,利用碳化矽(SiC)基板就有其必要。因此,能夠應對高壓、高溫以及高頻的優異特性成為新的半導體應用發展焦點。

基板內部結構技術

碳化矽(SiC)基板的內部結構必須非常正確,不能有瑕疵,請看圖1。

圖1(a)是一張正常碳化矽(SiC)晶體的示意圖,圖1(b)顯示碳化矽(SiC)晶體有缺陷。如果我們不能確保碳化矽(SiC)基板的品質,就無法製造出優良的碳化矽(SiC)晶片。因此,檢驗碳化矽(SiC)晶體內部結構的技術也變得非常重要。

目前關鍵的晶體缺陷只能以破壞性的KOH蝕刻方式進行抽樣檢測,...

清大動機系團隊成功開發「雷射低碳製造技術」:製程縮時、碳排大降!

為協助我國製造業強化製程優化能力,提升製造業生產產品之加工效率,國科會積極推動智慧製造創新技術研發。在國科會長期支持下,國立清華大學動力機械工程學系李明蒼教授團隊針對光電半導體產品開發出「雷射低碳製造技術」,可大幅縮短製程工序時間及材料成本,同時具備靈活的製程與設備整合彈性。

異質整合系列-2:先進封裝技術發展趨勢

北美智權報於異質整合系列-1:藍圖及應用概觀 一文中,已詳細介紹過異質整合技術的興起及願景,文中曾指出異質整合可以說是半導體未來的關鍵技術方向,雖然現在許多大廠 (如AMD、Intel、Samsung、華為)的處理器已應用了異質整合的系統級封裝技術,但還是有許多領域待摸索及發展的。本文藉由《 【35th MIC FORUM Fall】 賦能 》研討會,進一步探討異質整合封裝技術的發展現況及未來趨勢。

資策會產業情報研究所資深產業分析師鄭凱安於《 【35th MIC FORUM Fall】 賦能 》研討會中,發表了以「異質整合封裝技術與應用發展趨勢」為題的研究報告,首先從宏觀角度檢視整...

先進封裝技術大盤點

隨著行動通訊需求不斷提升,終端設備輕薄短小的需求也是與日俱增。在摩爾定律(Moore's law)已漸漸不適用於國際半導體技術發展路線圖預測的今天,要為半導體產業帶來突破性的發展,單靠將製程技術推向更細微化,從而再縮小裸晶尺寸的方式已顯然不足。除此之外,封裝技術的變革也是半導體技術發展的關鍵因素。

談到晶片尺寸微小化,大部分人都會著眼於製程技術,其實製程進步是有其極限的,不可能無止境的纏鬥下去;另一方面,晶片除了講究裸晶尺寸外,在電路板上的占位面積也很重要,這時候,封裝技術就是決勝關鍵。

大者恆大,小廠面臨被併購危機

在半導體製程技術上,不管是良率還是產能,台積電(TSMC)的5...

鍺的環保回收及先進半導體製程應用

鍺是一種半導體材質,電性質介於一般金屬和絕緣體之間,可用於製造電晶體和各種電子裝置,因此鍺的特性可應用於半導體、核物理探測、光纖通訊、紅外光學、軍用夜視鏡、太陽能電池、化學催化劑、生物醫學等終端應用。鍺也是重要的半導體材料,目前已經被用在半導體先進製程環繞式閘極(Gate all around: GAA)的製作中,以矽鍺磊晶的方式製成環繞式閘極電晶體。本文關注鍺在這方面相關應用及其環保回收綠色技術的國際間重要專利,啟發國內業者面對出口管制的因應措施,除了友岸外交、建立結盟網絡之外,強化綠色循環回收技藝不失為一個解決之道,同時從3奈米邁向2奈米先進半導體製造技術中,鍺在其中亦扮演關鍵角色。

...